# 1080p60 IMAGE SENSOR RECEIVER

Check for Samples: SN65LVDS324

### **FEATURES**

- Bridges the Interface Between Video Image Sensors and Processors

- Receives Aptina HiSPi<sup>™</sup>, Panasonic LVDS, or Sony LVDS Parallel; Outputs 1.8V CMOS with 10/12/14/16 Bits at 18.5MHz to 162MHz

- SubLVDS Inputs Support Up To 648Mbps

- Integrated 100Ω Differential Input Termination

- Test Image Generation Feature

- Compatible with TI OMAP™ and DaVinci™ Including DM385, DM8127, DM36x, and DMVA

- Low Power 1.8V CMOS Process

- Configurable Output Conventions

- Packaged in 4.5 x 7mm BGA

## **APPLICATIONS**

- IP Network Cameras

- Machine Vision

- Video Conferencing

- Gesture Recognition

#### DESCRIPTION

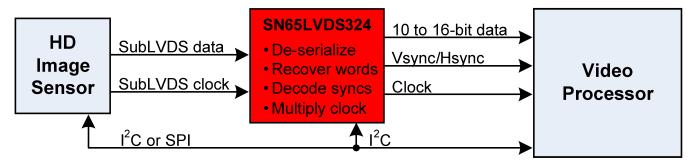

The SN65LVDS324 is a SubLVDS deserializer that recovers words, detects sync codes, multiplies the input DDR clock by a ratio, and outputs parallel CMOS 1.8V data on the rising clock edge. It bridges the video stream interface between HD image sensors made by leading manufacturers, to a format that common processors can accept. The supported pixel frequency is 18.5MHz to 162MHz — suitable for resolutions from VGA to 1080p60.

Four high-level modes are supported: Aptina 1-Channel 4-Lane, Aptina 1-Channel 2-Lane, Panasonic 2-Channel 2-Port, and Sony LVDS Parallel. Each supports 10/12/14/16 bit sub-modes, according to Table 1. Each mode also has a configurable allowable frequency range, as specified by Table 3 register PLL\_CFG.

The SN65LVDS324 is configured through its I<sup>2</sup>C-programmable registers. This volatile memory must be written after power up. Configuration options include the MSB/LSB output order, sync polarity convention, data slew rate, and two output timing modes (long-setup or clock-centered), for wider compatibility with different processors and software. The TESTMODE\_VIDEO feature is designed to assist engineering development. The max allowable frame size is 8191 x 8191.

With integrated differential input termination, and a footprint of 4.5 x 7mm, the SN65LVDS324 provides a differentiated solution with optimized form, function, and cost. It operates through an ambient temperature range of -40°C to 85°C.

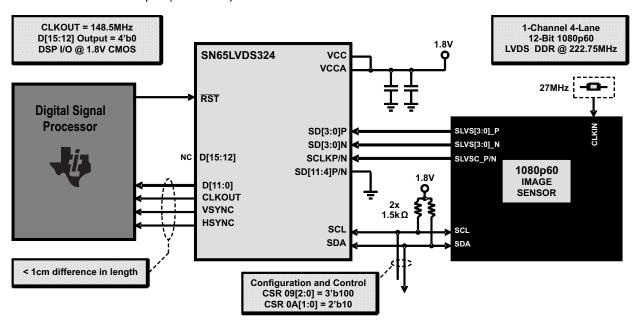

Figure 1. General System Diagram

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

OMAP, DaVinci are trademarks of Texas Instruments. HiSPi is a trademark of Aptina.

SLLSED9 -NOVEMBER 2012 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

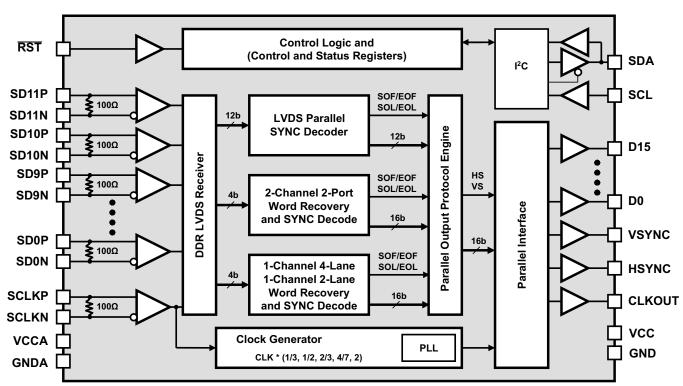

#### **FUNCTIONAL DESCRIPTION**

Figure 2. Functional Block Diagram

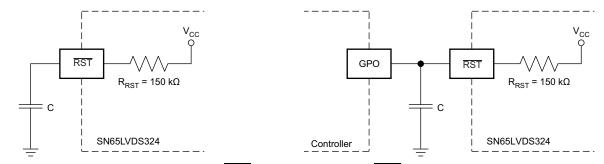

### **Reset Implementation**

When  $\overline{RST}$  is Low, the PLL is disabled, the <u>SubL</u>VDS inputs are disabled, and all outputs drive either  $V_{OH}$  or  $V_{OL}$  with no toggling. It is critical to transition the  $\overline{RST}$  input from a low to high level after the  $V_{CC}$  supply has reached the minimum recommended operating voltage. This is achieved by an external capacitor connected between  $\overline{RST}$  and GND, and/or by a control signal to the  $\overline{RST}$  input. Both implementations are shown:

Figure 3. External Capacitor Controlled RST

Figure 4. RST Input from Active Controller

#### **Device Configurations**

Table 1. SN65LVDS324 Modes, Common Frequencies, and Signals Used (1)(2)

| SENSOR_CFG<br>(CSR 09[2:0]) | SubLVDS<br>Interface<br>Mode | Bits<br>Per<br>Pixel | Target<br>Video | Target SCLK<br>Frequency<br>(MHz) | Target<br>PLL_CFG<br>(CSR 0A[1:0]) | Target<br>CLKOUT<br>Frequency<br>(MHz) | SCLK         | SD<br>[0:1] | SD2    | SD<br>[3:4]  | SD<br>[5:9] | SD<br>[10:11] |  |

|-----------------------------|------------------------------|----------------------|-----------------|-----------------------------------|------------------------------------|----------------------------------------|--------------|-------------|--------|--------------|-------------|---------------|--|

| 000                         | Sony                         | 10                   |                 |                                   |                                    |                                        | Sensor       | GND         |        |              |             |               |  |

| 001                         | LVDS<br>Parallel 12          | 12                   |                 | 74.25                             | 10                                 |                                        | Clock        | X[0:1]      | X[2]   | X[3:4]       | X[5:9]      | X[10:11]      |  |

| 010                         | Panasonic                    | 1000p                |                 | Sensor                            | Ch1                                | Sensor                                 | Ch2          |             |        |              |             |               |  |

| 011                         | 2-Channel<br>2-Port          |                      | 11              | 148.5                             | Ch1<br>Clock                       | X[0:1]                                 | Ch2<br>Clock | X[0:1]      |        | l            |             |               |  |

| 100                         | 1-Channel 1 4-Lane 1 Aptina  | Aptina 12            |                 | 222.75                            | 10                                 |                                        |              |             |        |              |             |               |  |

| 110                         |                              | 16                   |                 | 297                               | 11                                 |                                        |              |             | X[2]   | X[3],<br>GND | GND         | GND           |  |

| 101                         |                              | 14                   |                 | 129.9375                          | 00                                 |                                        | Sensor       |             | X[0:1] |              | OND         |               |  |

| 111                         |                              | 12                   | 720p<br>60fps   | 222.75                            | 10                                 | 74.25                                  | Clock        |             | GND    | GND          |             |               |  |

<sup>(1)</sup> X[0:11] represent the connected sensor's LVDS data lanes.

## **Aptina Mode Specifics**

Only the Streaming-SP HiSPi mode is supported. If "FLR" and "CRC" are in the data stream, the SN65LVDS324 will transmit them. "IDL" cannot match a sync code or be all-zero.

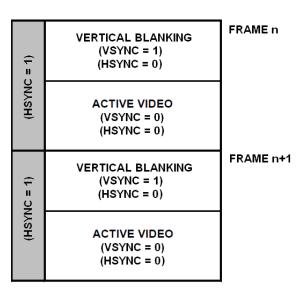

## **VSYNC and HSYNC Output Timing**

Figure 5 describes the horizontal and vertical blanking periods, and how they generally relate to the VSYNC and HSYNC outputs. The SN65LVDS324 asserts VSYNC (driven high) by default, and drives VSYNC high for at least one CLKOUT cycle at the beginning of each video frame. The SN65LVDS324 sensor interface logic determines the beginning of an active video frame by sensor-dependent methods.

There may be certain VSYNC and HSYNC operating requirements in the video processing pipeline in the DSP, such as a required number of vertical blanking lines, requirements for horizontal sync during vertical blanking, or requirements for data patterns during blanking times, special requirements for still image capture, etc. Systems that utilize SN65LVDS324 are required to configure the sensor to meet the vertical blanking and horizontal blanking requirements set by DSP video processing pipeline; these limitations shall be met by the sensor and not by SN65LVDS324 logic.

Figure 5. VSYNC and HSYNC Output Relation to Active Video Frames

<sup>(2)</sup> GND represents a connection to the system reference ground.

SLLSED9 -NOVEMBER 2012 www.ti.com

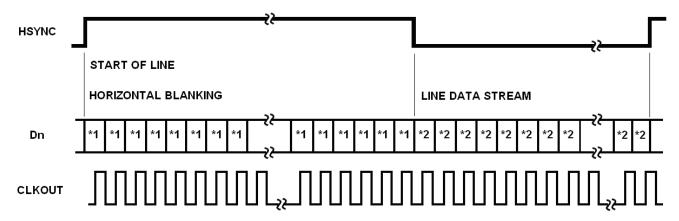

HSYNC is asserted (driven high) by default. HSYNC is driven low during the active video data stream transfer, as illustrated in Figure 6. HSYNC may be de-asserted (driven low) while VSYNC is asserted or de-asserted.

As shown in Figure 6, the HSYNC output is generally asserted following an EOL (End of Line) indication from the image sensor, and de-asserted (driven low) following a SOL (Start of Line) indication. Figure 6 further illustrates the data expected on the output interface during blanking periods.

<sup>\*1</sup> Output Dn during horizontal blanking is FFF0h for an active video line and FFFFh during vertical blanking (i.e. VSYNC=1)

Figure 6. HSYNC Output Relation to Line Data Stream

#### NOTE

The SN65LVDS324 overrides the fixed patterns illustrated in Figure 6 (FFF0h and FFFFh as shown by notes \*1 and \*2) when line data is received from the sensor during blanking periods.

#### Local I<sup>2</sup>C Interface Overview

The SCL and SDA terminals are used for I<sup>2</sup>C clock and I<sup>2</sup>C data, respectively. The SN65LVDS324 I<sup>2</sup>C interface conforms to the two-wire serial interface defined by the I<sup>2</sup>C Bus Specification, Version 2.1 (January 2000), and supports standard mode transfers up to 400 kbps.

The device address byte is the first byte received following the START condition from the master device. The 7 bit device address for SN65LVDS324 is factory preset to 7'b0101101 (0x2D). Table 2 clarifies the SN65LVDS324 target address.

Table 2. SN65LVDS324 I<sup>2</sup>C Target Address Description

| SN65LVDS324 I <sup>2</sup> C TARGET Address <sup>(1)</sup> |       |       |       |       |       |       |             |

|------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------------|

| Bit 7 (MSB)                                                | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (W/R) |

| 0                                                          | 1     | 0     | 1     | 1     | 0     | 1     | 0/1         |

<sup>(1)</sup> When ADDR=1, Address Cycle is 0x5A (Write) and 0x5B (Read)

The following procedure is followed to write to the SN65LVDS324 I<sup>2</sup>C registers:

- 1. The master initiates a write operation by generating a start condition (S), followed by the SN65LVDS324 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The SN65LVDS324 acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within SN65LVDS324) to be written, consisting of one byte of data, MSB-first.

Product Folder Links: SN65LVDS324

- 4. The SN65LVDS324 acknowledges the sub-address cycle.

- 5. The master presents the first byte of data to be written to the I<sup>2</sup>C register.

Submit Documentation Feedback

<sup>\*2</sup> Output Dn is pixel data for an active video line and FFFFh during vertical blanking (i.e. VSYNC=1)

- 6. The SN65LVDS324 acknowledges the byte transfer.

- 7. The master may continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the SN65LVDS324.

- 8. The master terminates the write operation by generating a stop condition (P).

The following procedure is followed to read the SN65LVDS324 I<sup>2</sup>C registers:

- 1. The master initiates a read operation by generating a start condition (S), followed by the SN65LVDS324 7-bit address and a one-value "W/R" bit to indicate a read cycle.

- 2. The SN65LVDS324 acknowledges the address cycle.

- 3. The SN65LVDS324 transmit the contents of the memory registers MSB-first starting at the last address specified.

- 4. The SN65LVDS324 will wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master after each byte transfer; the I<sup>2</sup>C master acknowledges reception of each data byte transfer.

- 5. If an ACK is received, the SN65LVDS324 transmits the next byte of data.

- 6. The master terminates the read operation by generating a stop condition (P).

## **Control and Status Registers Overview**

CSR's are accessible through the local I<sup>2</sup>C interface. Refer to Table 3 for SN65LVDS324 CSR descriptions. Reads from reserved fields not described return zeros, and writes are ignored.

CSR's "SENSOR\_CFG" and "PLL\_CFG" must be set before the input clock (SCLK) is applied.

Table 3. SN65LVDS324 CSR Bit Field Definitions

| ADDRESS     | BIT(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DESCRIPTION                                                                                                                                                                                                                                                                                            | ACCESS |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| 0x00 - 0x07 | 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DEVICE_ID Returns a string of ASCII characters "LVDS324" preceded by one space character. Addresses 0x00 - 0x07 = {0x20, 0x4C, 0x56, 0x44, 0x53, 0x33, 0x32, 0x34}                                                                                                                                     | R      |  |  |

| 0x08        | 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DEVICE_REV Device revision; returns 0x01                                                                                                                                                                                                                                                               | R      |  |  |

|             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SOFT_RESET This bit automatically clears when set to '1' and returns zeros when read. When set, the device is reset to the default condition.                                                                                                                                                          | RW     |  |  |

|             | TESTMODE_VIDEO When enabled, the device outputs a known color pattern with SCLK applied. The pattern is 128 lines of red, 128 of green, and 128 of blue, repeated. CSR addresses 0B, 0C, 0D, and 0E set the active image area, while addresses 1F, 20, 21, and 22 set the entire frame including blanking.  SENSOR_CFG and PLL_CFG control the bpp, PLL multiplier, and PLL range. The CLKOUT frequency directly scales the frame rate; for the default 2250x1100 frame, a CLKOUT frequency of 148.5MHz causes 60fps.  0 – Disabled (default) 1 – Enabled |                                                                                                                                                                                                                                                                                                        |        |  |  |

| 0x09        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LSB_FIRST_OUTPUT 0 - Output data is MSB first; D[15:0] output represents MSB at D0 1 - Output data is LSB first; D[15:0] output represents LSB at D0 (default)                                                                                                                                         | RW     |  |  |

|             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SYNC_ACTIVE_HIGH  0 - VSYNC and HSYNC are output low during blanking periods  1 - VSYNC and HSYNC are output high during blanking periods (default)                                                                                                                                                    |        |  |  |

|             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLK_CENTERED_TIMING 0 - Output timing accommodates long setup time receivers [e.g. DaVinci] (default) 1 - Outputs are clock-centered for relatively matched setup/hold receivers [e.g. OMAP]                                                                                                           | RW     |  |  |

|             | 2:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SENSOR_CFG This field shall be written to configure the sensor interface per Table 1.  000 – LVDS Parallel 10bpp mode (default) 001 – LVDS Parallel 12bpp mode 010 – 2-Channel 2-Port 12bpp mode 010 – 2-Channel 2-Port 16bpp mode 011 – 1-Channel 2-Lane 16bpp mode 011 – 1-Channel 2-Lane 12bpp mode | RW     |  |  |

(1) R = Read Only; RW = Read/Write (only reads return undetermined values)

## Table 3. SN65LVDS324 CSR Bit Field Definitions (continued)

| ADDRESS | BIT(S) | D                                                                                            | ESCRIPTION                                             | ACCESS |

|---------|--------|----------------------------------------------------------------------------------------------|--------------------------------------------------------|--------|

|         |        | CLKOUT_PLL_LOCK                                                                              |                                                        |        |

|         | 7      | 0 - Output pixel clock PLL not locked                                                        |                                                        | R      |

|         |        | 1 – Output pixel clock PLL locked                                                            |                                                        |        |

| _       | 6      | VCM_MODE 0 - Selects Low common mode voltage rang                                            | 0                                                      | RW     |

|         | 0      | 1 – Selects High common mode voltage rang                                                    |                                                        | IXVV   |

|         |        | D_SLEW_RATE                                                                                  |                                                        |        |

|         |        | Controls the rise and fall time for D[15:0].                                                 |                                                        |        |

|         | 5:4    | 00 – Slowest; sets to 50% of the baseline sp<br>01 – Slower; sets to 75% of the baseline spe |                                                        | RW     |

|         |        | 10 – Baseline (default)                                                                      | ou .                                                   |        |

|         |        | 11 - Fastest; sets to 150% of the baseline sp                                                | peed                                                   |        |

|         |        | PLL_CFG                                                                                      |                                                        |        |

|         |        | This field sets the allowable SCLK frequency register defaults to 10 (and 01 for the 14bpp   | range, based on the mode set by SENSOR_CFG. The mode). |        |

|         |        | LVDS Parallel 10/12bpp (PLL Multiplier = 2)                                                  |                                                        |        |

|         |        | 00 - SCLK = 18.5 to 33MHz,                                                                   | CLKOUT = 37 to 66MHz                                   |        |

|         |        | 01 - SCLK = 31 to 60MHz,                                                                     | CLKOUT = 62 to 120MHz                                  |        |

|         |        | 10 - SCLK = 58 to 81MHz,                                                                     | CLKOUT = 116 to 162MHz                                 |        |

|         |        | 11 – Reserved                                                                                |                                                        |        |

|         |        | 2-Channel 2-Port 12bpp and 1-Channel 4-                                                      | ane 12bpp (PLL Multiplier = 2/3)                       |        |

| 0x0A    |        | 00 - SCLK = 55.5  to  99MHz,                                                                 | CLKOUT = 37 to 66MHz                                   |        |

|         |        | 01 - SCLK = 97  to  180MHz,                                                                  | CLKOUT = 64.7 to 120MHz                                |        |

|         |        | 10 – SCLK = 178 to 243MHz,                                                                   | CLKOUT = 118.7 to 162MHz                               |        |

|         |        | 11 – Reserved                                                                                |                                                        |        |

|         | 1:0    | 2-Channel 2-Port 16bpp and 1-Channel 4-                                                      | ane 16bpp (PLL Multiplier = 1/2)                       | RW     |

|         |        | 00 - SCLK = 74  to  120MHz,                                                                  | CLKOUT = 37 to 60MHz                                   |        |

|         |        | 01 – SCLK = 118 to 180MHz,                                                                   | CLKOUT = 59 to 90MHz                                   |        |

|         |        | 10 – SCLK = 178 to 222MHz,                                                                   | CLKOUT = 89 to 111MHz                                  |        |

|         |        | 11 – SCLK = 220 to 324MHz,                                                                   | CLKOUT = 110 to 162MHz                                 |        |

|         |        | 1-Channel 4-Lane 14bpp (PLL Multiplier = 4                                                   | <i>(</i> 7)                                            |        |

|         |        | 00 - SCLK = 120 to 220MHz,                                                                   | CLKOUT = 68.6 to 125.7MHz                              |        |

|         |        | 01 – SCLK = 218 to 283.5MHz,                                                                 | CLKOUT = 124.6 to 162MHz                               |        |

|         |        | 10 – Reserved                                                                                |                                                        |        |

|         |        | 11 – Reserved                                                                                |                                                        |        |

|         |        | 1-Channel 2-Lane 12bpp (PLL Multiplier = 1                                                   | /3)                                                    |        |

|         |        | 00 - SCLK = 55.5  to  99MHz,                                                                 | CLKOUT = 18.5 to 33MHz                                 |        |

|         |        | 01 – SCLK = 97 to 180MHz,                                                                    | CLKOUT = 32.3 to 60MHz                                 |        |

|         |        | 10 – SCLK = 178 to 297MHz,                                                                   | CLKOUT = 59.3 to 99MHz                                 |        |

|         |        | 11 – Reserved                                                                                |                                                        |        |

## Table 3. SN65LVDS324 CSR Bit Field Definitions (continued)

| ADDRESS     | BIT(S) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                            | ACCESS<br>(1) |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 0x0B        | 4:0    | FRAME_WIDTH_MSB The width of the active area; this field is the high order byte. The default is 1920 (0x <b>07</b> 80), and this field's default is 0x07. The max width is 8191. When TESTMODE_VIDEO is disabled, this field is only used to set SENSOR_SPECIFIC registers that flag window size errors.                                                                                               | RW            |

| 0x0C        | 7:0    | FRAME_WIDTH_LSB The width of the active area; this field is the low order byte. The default is 1920 (0x07 <b>80</b> ), and this field's default is 0x80. The max width is 8191. When TESTMODE_VIDEO is disabled, this field is only used to set SENSOR_SPECIFIC registers that flag window size errors.                                                                                                | RW            |

| 0x0D        | 4:0    | FRAME_HEIGHT_MSB The height of the active area; this field is the high order byte. The default is 1080 (0x <b>04</b> 38), and this field's default is 0x04. The max height is 8191. When TESTMODE_VIDEO is disabled, this field is only used to set SENSOR_SPECIFIC registers that flag window size errors. In LVDS Parallel modes, the height must include all lines between SAV-Valid and EAV-Valid. | RW            |

| 0x0E        | 7:0    | FRAME_HEIGHT_LSB The height of the active area; this field is the low order byte. The default is 1080 (0x0438), and this field's default is 0x38. The max height is 8191. When TESTMODE_VIDEO is disabled, this field is only used to set SENSOR_SPECIFIC registers that flag window size errors. In LVDS Parallel modes, the height must include all lines between SAV-Valid and EAV-Valid.           | RW            |

| 0x0F - 0x1E | 7:0    | SENSOR_SPECIFIC These are sensor-specific status registers, and depend on SENSOR_CFG. They are further described by Table 4 through Table 6.                                                                                                                                                                                                                                                           | RW            |

| 0x1F        | 4:0    | TESTMODE_WIDTH_MSB Applies only when TESTMODE_VIDEO is enabled, and configurable up to 8191 pixels. This field controls the high order byte of the frame width including blanking; the default is 2250 (0x08CA), and this field's default is 0x08. For 720p, a width of 1500 (0x <b>05</b> DC) facilitates 60fps with 74.25MHz.                                                                        | RW            |

| 0x20        | 7:0    | TESTMODE_WIDTH_LSB Applies only when TESTMODE_VIDEO is enabled, and configurable up to 8191 pixels. This field controls the low order byte of the frame width including blanking; the default is 2250 (0x08CA), and this field's default is 0xCA. For 720p, a width of 1500 (0x05DC) facilitates 60fps with 74.25MHz.                                                                                  | RW            |

| 0x21        | 4:0    | TESTMODE_HEIGHT_MSB Applies only when TESTMODE_VIDEO is enabled, and configurable up to 8191 pixels. This field controls the high order byte of the frame height including blanking; the default is 1100 (0x <b>04</b> 4C), and this field's default is 0x04. For 720p, a height of 825 (0x <b>03</b> 39) facilitates 60fps with 74.25MHz.                                                             | RW            |

| 0x22        | 7:0    | TESTMODE_ HEIGHT_LSB Applies only when TESTMODE_VIDEO is enabled, and configurable up to 8191 pixels. This field controls the low order byte of the frame height including blanking; the default is 1100 (0x044C), and this field's default is 0x4C. For 720p, a height of 825 (0x0339) facilitates 60fps with 74.25MHz.                                                                               | RW            |

| 0x23 - 0x30 | 7:0    | RESERVED These registers are reserved for factory test. Do not write to them.                                                                                                                                                                                                                                                                                                                          | RW            |

Product Folder Links: SN65LVDS324

# Table 4. Sensor-Specific Registers for Aptina Modes

| ADDRESS | BIT(S) | DESCRIPTION                                                                                                                                                                                   | ACCESS <sup>(1)</sup> |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0.05    | 6      | FILLER_EN 0 – FLR codes are not used in data stream 1 – FLR codes are used in data stream (default)                                                                                           | RW                    |

| 0x0F    | 5      | CRC_EN 0 - CRC is not used in the data stream 1 - CRC is used in the data stream (default)                                                                                                    | RW                    |

|         | 7      | CLEAR_STATUS When a '1' is written to this field, the status bits in 0x10 and 0x11 are cleared, and this bit is auto-cleared to a zero value (always returns zero when read)                  | W                     |

| 0x10    | 3      | CRC_ERR_LANE3 0 - No checksum error detected (default) 1 - Checksum error detected Note: Bits in registers 0x10 and 0x11 are latched and cleared only when the CLEAR_STATUS field is written. | R                     |

|         | 2      | CRC_ERR_LANE2; same bit function as CRC_ERR_LANE3 but applied to LANE 2.                                                                                                                      | R                     |

|         | 1      | CRC_ERR_LANE1; same bit function as CRC_ERR_LANE3 but applied to LANE 1.                                                                                                                      | R                     |

|         | 0      | CRC_ERR_LANE0; same bit function as CRC_ERR_LANE3 but applied to LANE 0.                                                                                                                      | R                     |

|         | 5      | UNKNOWN_SYNC_CODE 0 - No unexpected sync code (default) 1 - Sync code (final word of sync_code) does not match a defined type                                                                 | R                     |

| 0v11    | 4      | SOF_ERR 0 – No SOF error occurred (default) 1 – SOF was detected when it was unexpected                                                                                                       | R                     |

| 0x11    | 3      | SOL_ERR 0 - No SOL error occurred (default) 1 - SOL was detected when it was unexpected                                                                                                       | R                     |

|         | 2      | SOV_ERR 0 - No SOV error occurred (default) 1 - SOV was detected when it was unexpected                                                                                                       | R                     |

<sup>(1)</sup> R = Read Only; RW = Read/Write; W = Write Only (reads return undetermined values)

## Table 5. Sensor-Specific Registers for Panasonic Modes

| ADDRESS | BIT(S) | DESCRIPTION                                                                                                                                                                              | ACCESS <sup>(1)</sup> |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0x0F    | 7:0    | Reserved.                                                                                                                                                                                | R                     |

| 0x10    | 7      | CLEAR_STATUS When a '1' is written to this field, the status bits in 0x11 are cleared, and this bit is auto-cleared to a zero value (always returns zero when read)                      | W                     |

|         | 7      | FRAME_SIZE_ERROR  0 – Start up sequence has not identified a frame size error, decode window applied.  1 – Start up sequence identified a frame size error, decode window is not applied | R                     |

|         | 5      | UNKNOWN_SYNC_CODE When set to'1', sync code (final word of sync_code) does not match a defined type                                                                                      | R                     |

| 0x11    | 4      | SOF_ERR When set to '1', SOF was detected when it was unexpected per the decode window.                                                                                                  | R                     |

|         | 3      | SOL_ERR When set to '1', SOL was detected when it was unexpected per the decode window.                                                                                                  | R                     |

| _       | 1      | EOF_ERR When set to '1', EOF was detected when it was unexpected per the decode window.                                                                                                  | R                     |

|         | 0      | EOL_ERR When set to '1', EOL was detected when it was unexpected per the decode window.                                                                                                  | R                     |

(1) R = Read Only; W = Write Only

## Table 6. Sensor-Specific Registers for Sony Modes

| ADDRESS | BIT(S) | DESCRIPTION                                                                                                                                                                              | ACCESS <sup>(1)</sup> |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0x0F    | 7:0    | Reserved.                                                                                                                                                                                | R                     |

| 0x10    | 7      | CLEAR_STATUS  When a '1' is written to this field, the status bits in 0x11 are cleared, and this bit is auto-cleared to a zero value (always returns zero when read)                     | W                     |

|         | 7      | FRAME_SIZE_ERROR  0 – Start up sequence has not identified a frame size error, decode window applied.  1 – Start up sequence identified a frame size error, decode window is not applied | R                     |

|         | 5      | UNKNOWN_SYNC_CODE When set to '1', sync code (final word of sync_code) does not match a defined type                                                                                     | R                     |

| 0x11    | 4      | SAV_VALID_ERR When set to '1', SAV (Valid Line) was unexpectedly detected per the decode window.                                                                                         | R                     |

|         | 3      | SAV_INVALID_ERR When set to '1', SAV (Invalid Line) was unexpectedly detected per the decode window.                                                                                     | R                     |

|         | 1      | EAV_VALID_ERR When set to '1', EAV (Valid Line) was unexpectedly detected per the decode window.                                                                                         | R                     |

|         | 0      | EAV_INVALID_ERR When set to '1', EAV (Invalid Line) was unexpectedly detected per the decode window.                                                                                     | R                     |

(1) R = Read Only; W = Write Only (reads return undetermined values)

SLLSED9 -NOVEMBER 2012 www.ti.com

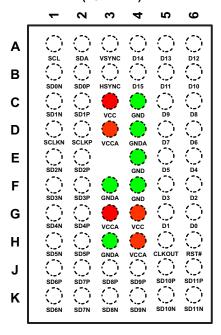

#### **PIN FUNCTIONS**

|             | PIN                                | DECORPTION                                                                                                                                                                                               |

|-------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL      | I/O                                | DESCRIPTION                                                                                                                                                                                              |

| SD[11:0]P/N | SubLVDS Input                      | SubLVDS Input Data Lanes with 100Ω differential termination. In the 2-Channel 2-Port configurations, SD2P/N is used as Channel 2 clock. See Table 1 for sensor SubLVDS signal mapping per configuration. |

| SCLKP/N     | (Failsafe)                         | SubLVDS Input Clock. In 2-Channel 2-Port mode, this input is the Channel 1 clock.                                                                                                                        |

| D[15:0]     |                                    | Parallel Output Pixel Data. Pixel data outputs beyond the pixel data width configuration are driven low.                                                                                                 |

| CLKOUT      | omeo output                        | Parallel Output Clock.                                                                                                                                                                                   |

| HSYNC       |                                    | Parallel Output Horizontal Sync.                                                                                                                                                                         |

| VSYNC       |                                    | Parallel Output Vertical Sync.                                                                                                                                                                           |

| SCL         | CMOS Input                         | Local I <sup>2</sup> C Programming Interface Clock Signal.                                                                                                                                               |

| RST         | (Failsafe)                         | Logic Reset. Active when Low.                                                                                                                                                                            |

| SDA         | CMOS<br>Input/Output<br>(Failsafe) | Local I <sup>2</sup> C Programming Interface Data Signal.                                                                                                                                                |

| GNDA        |                                    | Reference Ground for Analog Circuits.                                                                                                                                                                    |

| VCCA        | Dower Supply                       | 1.8V Power Supply for Analog Circuits.                                                                                                                                                                   |

| GND         | Power Supply                       | Reference Ground for Digital Circuits.                                                                                                                                                                   |

| VCC         |                                    | 1.8V Power Supply for Digital Circuits.                                                                                                                                                                  |

## **ORDERING INFORMATION**

| PART NUMBER     | PART MARKING | PACKAGE / SHIPPING <sup>(1)</sup> |

|-----------------|--------------|-----------------------------------|

| SN65LVDS324ZQLR | LVDS324      | 59-ball PBGA / Reel               |

(1) For the most current package and ordering information, see the TI web site at www.ti.com.

Product Folder Links: SN65LVDS324

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                         |                                    | VALUE         | UNITS |

|-------------------------|------------------------------------|---------------|-------|

| Supply Voltage Range    | V <sub>CCA</sub> , V <sub>CC</sub> | -0.3 to 2.175 | V     |

| Input Voltage Range     | All Input Terminals                | -0.5 to 2.175 | ٧     |

| Storage temperature     | T <sub>S</sub>                     | -65 to 150    | ů     |

| Floatroototic discharge | Human Body Model (2)               |               | 147   |

| Electrostatic discharge | Charged-device model (3)           | ±1.5          | KV    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted) (1)

|                       | PARAMETER                               | TEST CONDITIONS                                                                             | MIN | TYP  | MAX | UNIT |

|-----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|-----|------|-----|------|

| $\theta_{JA}$         | Junction-to-free-air thermal resistance | High-K JEDEC test board, 2s2p (double signal layer, double buried power plane), no air flow |     | 73.9 |     | °C/W |

| $\theta_{\text{JCT}}$ | Junction-to-case-top thermal resistance | Cu cold plate measurement process                                                           |     | 30.6 |     | °C/W |

| $\theta_{JB}$         | Junction-to-board thermal resistance    | EIA/JESD 51-8                                                                               |     | 37.7 |     | °C/W |

| ΨЈТ                   | Junction-to-top of package              | EIA/JESD 51-2                                                                               |     | 1.3  |     | °C/W |

| ΨЈВ                   | Junction-to-board                       | EIA/JESD 51-6                                                                               |     | 36.9 |     | °C/W |

| $T_{J}$               | Junction temperature                    |                                                                                             |     |      | 125 | °C   |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                      |                                                      |                           | MIN  | NOM  | MAX  | UNIT |  |

|----------------------|------------------------------------------------------|---------------------------|------|------|------|------|--|

| $V_{CCA}$            | Power supply; analog circuits                        |                           | 1.65 | 1.8  | 1.95 | V    |  |

| V <sub>CC</sub>      | Power supply; digital circuits                       |                           | 1.65 | 1.8  | 1.95 | V    |  |

| V                    | Dower cumply volte as noise                          | f <sub>NOISE</sub> < 1MHz |      |      |      | m)/  |  |

| V <sub>CCn(PP)</sub> | Power supply voltage noise                           | f <sub>NOISE</sub> > 1MHz |      |      | 40   | mV   |  |

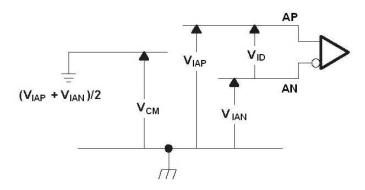

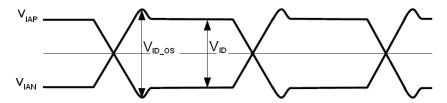

| V <sub>ID</sub>      | Magnitude of differential input voltage; see F       | 90                        |      | 350  | mV   |      |  |

|                      | Level consequence of the second Figure 7             | CSR 0A[6] = 0             | 100  |      | 650  | mV   |  |

| $V_{CM}$             | Input common mode voltage; see Figure 7              | CSR 0A[6] = 1             | 550  |      | 1200 |      |  |

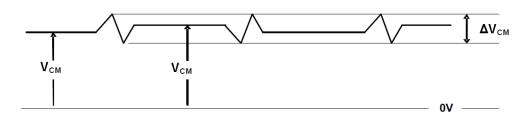

| V <sub>CM</sub>      | Peak to peak input common mode voltage v             |                           |      | 50   | mV   |      |  |

| V <sub>IN_DC</sub>   | SubLVDS receiver input voltage range                 |                           |      | 1400 | mV   |      |  |

| V <sub>ID_OS</sub>   | Differential input voltage overshoot/undersho        |                           |      | 20%  |      |      |  |

| T <sub>A</sub>       | Operating free-air temperature                       | -40                       |      | 85   | °C   |      |  |

| T <sub>CASE</sub>    | Case temperature                                     |                           |      | 101  | °C   |      |  |

| f <sub>I2C</sub>     | Local I <sup>2</sup> C interface operating frequency |                           |      |      | 400  | kHz  |  |

| f <sub>CLK</sub>     | SubLVDS input clock (SCLKP/N) frequency              |                           | 18.5 |      | 324  | MHz  |  |

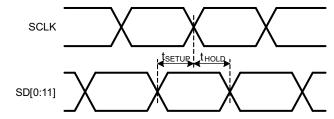

|                      | SubLVDS data setup time to SCLKP/N                   | LVDS Parallel modes       | 1500 |      |      |      |  |

| t <sub>SETUP</sub>   | transition; see Figure 10                            | All other modes           | 350  |      |      | ps   |  |

|                      | SubLVDS data hold time after SCLKP/N                 | LVDS Parallel modes       | 1500 |      |      |      |  |

| t <sub>HOLD</sub>    | transition; see Figure 10                            | All other modes           | 350  |      |      | ps   |  |

| t <sub>DUTCLK</sub>  | SubLVDS CLK input clock duty cycle                   | 45%                       |      | 55%  |      |      |  |

| C <sub>L</sub>       | Parallel output load capacitance <sup>(1)</sup>      |                           |      | 5    | 6    | pF   |  |

<sup>(1)</sup> The SN65LVDS324 supports up to 10pF parallel output load capacitance under test conditions.

<sup>(2)</sup> Tested in accordance with JEDEC Standard 22, Test Method A114-B

<sup>(3)</sup> Tested in accordance with JEDEC Standard 22, Test Method C101-A

### DC ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                       | TEST CONDITIONS                                                                           | MIN                 | TYP <sup>(1)</sup> | MAX                 | UNIT |

|-------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------|------|

| $V_{THL}$         | Low-level differential input voltage threshold  | V V V                                                                                     | -40                 |                    |                     | mV   |

| $V_{THH}$         | High-level differential input voltage threshold | V <sub>SD[11:0]P</sub> - V <sub>SD[11:0]N</sub> , V <sub>SCLKP</sub> - V <sub>SCLKN</sub> |                     |                    | 40                  | mV   |

| $V_{IL}$          | Low-level control signal input voltage          | SCL, SDA                                                                                  |                     |                    | 0.3×V <sub>CC</sub> | V    |

| $V_{IH}$          | High-level control signal input voltage         | SCL, SDA                                                                                  | 0.7×V <sub>CC</sub> |                    |                     | V    |

| $V_{OH}$          | High-level output voltage                       | $I_{OH} = -2 \text{ mA}$                                                                  | 1.3                 |                    |                     | V    |

| V <sub>OL</sub>   | Low-level output voltage                        | I <sub>OL</sub> = 2 mA                                                                    |                     |                    | 0.4                 | V    |

| Ios               | Short circuit output current                    | Output V <sub>OH</sub> driving GND short                                                  | -35                 |                    |                     | mA   |

| I <sub>LEAK</sub> | Failsafe input leakage current                  | $V_{CC} = 0; V_{CC(PIN)} = 1.8 \text{ V}$                                                 |                     |                    | 10                  | μΑ   |

| I <sub>IH</sub>   | High level input current                        | CDA CCI                                                                                   |                     |                    | 5                   | μΑ   |

| I <sub>IL</sub>   | Low level input current                         | SDA, SCL                                                                                  |                     |                    | 5                   | μΑ   |

|                   |                                                 | LVDS Parallel 1080p60                                                                     |                     | 89                 | 125                 |      |

| I <sub>CC</sub>   | Active current <sup>(2)</sup> (3)               | 2-Channel 2-Port 1080p60<br>1-Channel 4-Lane 1080p60                                      |                     | 83                 | 120                 | mA   |

|                   |                                                 | 1-Channel 2-Lane 720p60                                                                   |                     | 74                 | 100                 |      |

| R <sub>DIFF</sub> | Differential termination resistance             |                                                                                           | 80                  | 100                | 125                 | Ω    |

| R <sub>RST</sub>  | Reset input resistance                          |                                                                                           | 120                 | 150                | 180                 | kΩ   |

| C <sub>IN</sub>   | Input pin capacitance                           |                                                                                           |                     | 1.5                |                     | pF   |

### **SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                                                               | TEST CONDITIONS                                   | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|--------------------|------|------|--|--|

| F <sub>CLKOUT</sub> | CLKOUT frequency                                                                                        | C <sub>L</sub> = 6 pF                             | 18.5 |                    | 162  | MHz  |  |  |

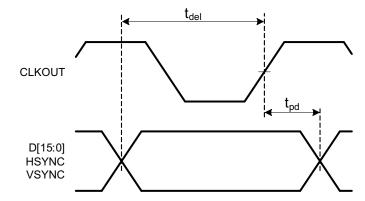

|                     | Data valid to CLKOLITA (and Figure 11)                                                                  | C <sub>L</sub> = 6 pF; CSR 09[3] = 1              | 1.5  |                    |      |      |  |  |

| t <sub>del</sub>    | Data valid to CLKOUT↑ (see Figure 11)                                                                   | C <sub>L</sub> = 6 pF; CSR 09[3] = 0              | 3.8  |                    |      | ns   |  |  |

|                     | CLKOUT↑ to data switching (see Figure 11)                                                               | C <sub>L</sub> = 6 pF; CSR 09[3] = 1              | 1.5  |                    |      |      |  |  |

| t <sub>pd</sub>     | CEROOT   to data switching (see Figure 11)                                                              | C <sub>L</sub> = 6 pF; CSR 09[3] = 0              | 0.2  |                    |      | ns   |  |  |

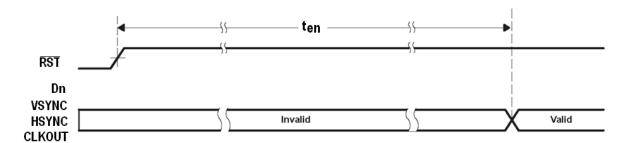

| t <sub>en</sub>     | Enable time, $\overline{\text{RST}}\uparrow$ to output valid and CLKOUT meets electrical specifications | F <sub>CLKOUT</sub> = 148.5 MHz,<br>See Figure 12 |      |                    | 2    | ms   |  |  |

| t <sub>r</sub>      | Rise transition time, output (20% to 80%)                                                               | C <sub>L</sub> = 6 pF, CSR 0A[5:4] = 10           | 450  | 750                | 1300 | ps   |  |  |

| t <sub>f</sub>      | Fall transition time, output (80% to 20%)                                                               | C <sub>L</sub> = 6 pF, CSR 0A[5:4] = 10           | 450  | 750                | 1300 |      |  |  |

| t <sub>dc</sub>     | CLKOUT duty cycle                                                                                       |                                                   | 45%  |                    | 55%  |      |  |  |

| tj                  | CLKOUT residual jitter                                                                                  | Peak to peak                                      |      |                    | 370  | ps   |  |  |

(1) All typical values are at  $V_{CC}$  = 1.8V and  $T_A$  = 25°C.

$<sup>\</sup>begin{array}{ll} \hbox{(1)} & \hbox{All typical values are at $V_{CC}=1.8$V$ and $T_A=25^\circ$C$} \\ \hbox{(2)} & V_{CC}=1.95$V; $T_A=0^\circ$C; $C_L=6p$F; Worst case test pattern \\ \hbox{(3)} & V_{CC}=1.8$V; $T_A=25^\circ$C; $C_L=5p$F; Typical power test pattern \\ \end{array}$

Figure 7. SubLVDS Input Voltage Definitions

Figure 8. SubLVDS Delta Common Mode Input Voltage Definition

Figure 9. V<sub>ID</sub> Overshoot Definition

Figure 10. SubLVDS Timing Definitions

SLLSED9 -NOVEMBER 2012 www.ti.com

Figure 11. CMOS Output Timing Waveforms

Figure 12. Device Enable Waveforms

#### TYPICAL APPLICATIONS

The SN65LVDS324 offers several operating modes, as described in this section. The typical mode of 1080p60 involves a 148.5MHz output clock.

The parallel output video interface provides up to 16-bits of data per pixel, a vertical synchronization signal (VSYNC), and a horizontal synchronization signal (HSYNC) that are all synchronous to the output clock, CLKOUT. VSYNC and HSYNC are by default logically active high, and output a high logic level during blanking periods.

The following application diagrams illustrate each high-level typical configuration given in Table 1.

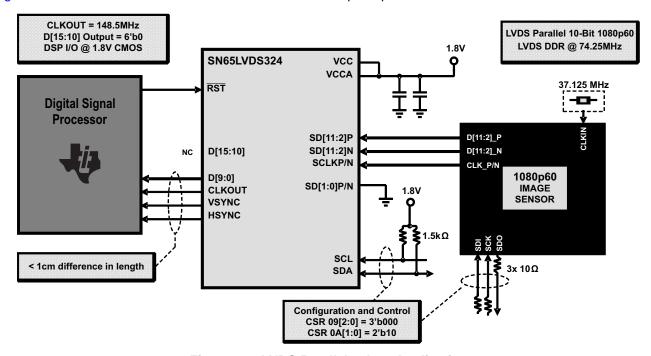

### Sony LVDS Parallel 10-Bit Mode

Figure 13 illustrates the LVDS Parallel 10-bit mode for 1080p60 operation.

Figure 13. LVDS Parallel 10bpp Application

In this configuration, the image sensor transmits 10-bit video with a DDR reference clock operating at 74.25MHz. The SN65LVDS324 provides a 2x PLL to convert the 74.25MHz SubLVDS input to a 148.5MHz pixel clock output (CLKOUT) for the 10-bit output interface.

An SPI-like serial bus is used to configure and control the sensor in this typical application example. The DSP shall properly configure the sensor to the particular target application, which may involve setting the electrical interface and optical gain settings.

The SN65LVDS324 identifies sync codes from the data stream to identify vertical and horizontal sync conditions, and sets the outputs HSYNC and VSYNC appropriately.

Product Folder Links: SN65LVDS324

SLLSED9 -NOVEMBER 2012 www.ti.com

## TYPICAL APPLICATIONS (continued)

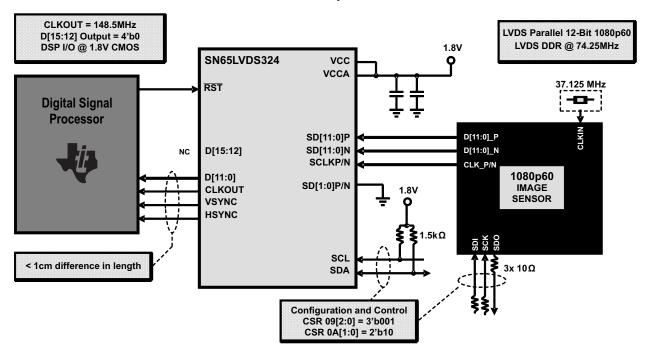

## Sony LVDS Parallel 12-Bit Mode

Figure 14 illustrates the 12-bit LVDS Parallel mode for 1080p60 operation. This mode operates identically to the LVDS Parallel 10-bit mode other than the data width and sync codes.

Figure 14. LVDS Parallel 12bpp Application

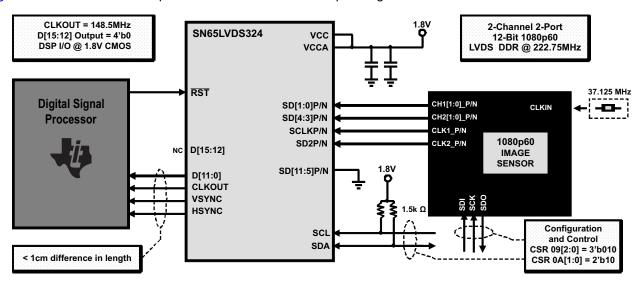

#### Panasonic 2-Channel 2-Port 12-Bit Mode

Figure 15 illustrates the 1080p60 2-Channel 2-Port 12-bit operating mode.

Figure 15. 2-Channel 2-Port 12bpp Application

The channel 2 clock is **not** guaranteed to be synchronous with channel 1; the SN65LVDS324 Word Alignment function provides the data synchronization between channel 1 and channel 2. If the sensor output is dual-frame WDR, the SN65LVDS324 transmits the data for both frames.

### TYPICAL APPLICATIONS (continued)

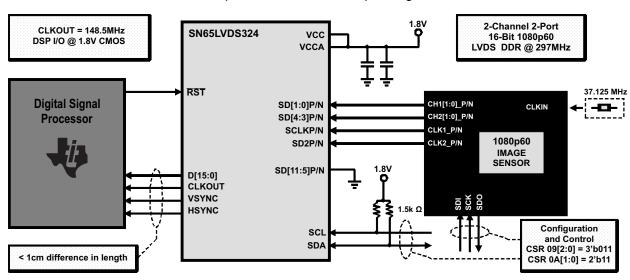

#### Panasonic 2-Channel 2-Port 16-bit Mode

Figure 16 illustrates the 16-bit color 1080p60 2-Channel 2-Port operating mode.

Figure 16. 2-Channel 2-Port 16bpp Application

## Aptina 1-Channel 4-Lane 12-bit Mode

Figure 17 illustrates the 1080p60 1-Channel 4-Lane 12-bit per pixel operating mode with an image sensor pixel clock frequency is 148.5MHz (222.75MHz SubLVDS clock frequency). In this configuration, the SN65LVDS324 outputs the parallel pixel clock (CLKOUT) at 148.5MHz by implementing a PLL operating with a 2/3 multiplier from the SubLVDS clock input (SCLKP/N).

Figure 17. 1-Channel 4-Lane 12bpp Application

SLLSED9 -NOVEMBER 2012 www.ti.com

## TYPICAL APPLICATIONS (continued)

## **Aptina 1-Channel 4-Lane 14-bit Mode**

Figure 18 illustrates the 1080p60 1-Channel 4-Lane 14-bit per pixel operating mode. Some image sensors utilize a compression method in 14-bit mode that communicates compressed data in 14 bits per pixel that can be expanded to 16 or 20 bits per pixel by the DSP video processing pipeline.

Figure 18. 1-Channel 4-Lane 14bpp Application

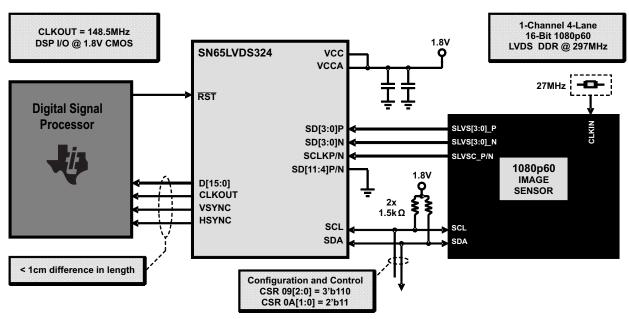

## Aptina 1-Channel 4-Lane 16-bit Mode

Figure 19 illustrates the 1080p60 1-Channel 4-Lane 16-bit per pixel operating mode.

Figure 19. 1-Channel 4-Lane 16bpp Application

## **TYPICAL APPLICATIONS (continued)**

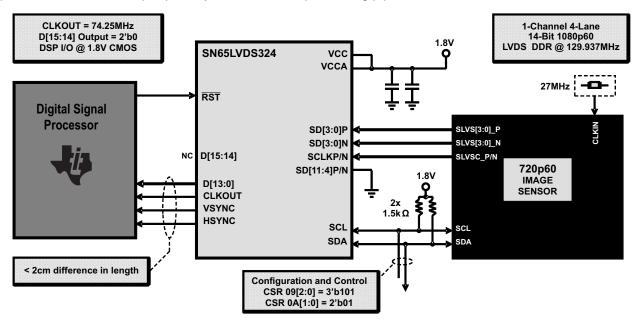

## **Aptina 1-Channel 2-Lane 12-bit Mode**

Figure 20 illustrates the 720p60 1-Channel 2-Lane 12-bit per pixel operating mode.

Figure 20. 1-Channel 2-Lane 12bpp Application

## **Decoupling Recommendations**

To minimize the power supply noise floor, provide good decoupling near the SN65LVDS324 power pins. The use of four ceramic capacitors (2x 0.01  $\mu$ F and 2x 0.1  $\mu$ F) provides good performance. At the very least, it is recommended to install one 0.1  $\mu$ F and one 0.01  $\mu$ F capacitor near the SN65LVDS324. To avoid large current loops and trace inductance, the trace length between decoupling capacitors and device power inputs pins must be minimized. Placing the capacitor underneath the SN65LVDS324 on the bottom of the PCB is often a good choice.

Product Folder Links: SN65LVDS324

## PACKAGE OPTION ADDENDUM

24-.lan-2013

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type               | Package<br>Drawing |    | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|----------------------------|--------------------|----|-------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

| SN65LVDS324ZQLR  | ACTIVE | BGA<br>MICROSTAR<br>JUNIOR | ZQL                | 59 | 1000        | Green (RoHS<br>& no Sb/Br) | Call TI          | Level-3-260C-168 HR | -40 to 85    | LVDS324           | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com 26-Jan-2013

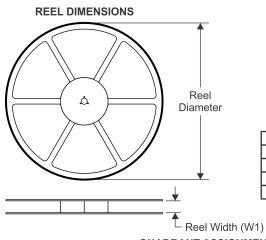

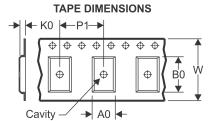

## TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type                  | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|----------------------------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65LVDS324ZQLR | BGA MI<br>CROSTA<br>R JUNI<br>OR | ZQL                | 59 | 1000 | 330.0                    | 16.4                     | 4.8        | 7.3        | 1.5        | 8.0        | 16.0      | Q1               |

www.ti.com 26-Jan-2013

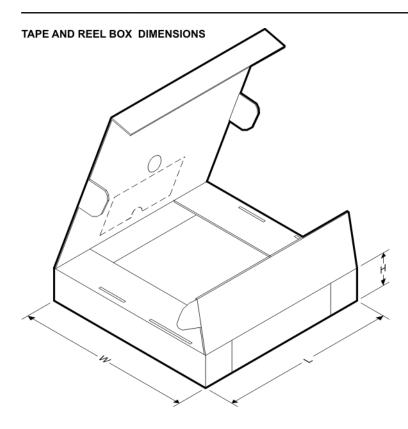

### \*All dimensions are nominal

| Device          | Package Type            | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|-------------------------|-----------------|------|------|-------------|------------|-------------|

| SN65LVDS324ZQLR | BGA MICROSTAR<br>JUNIOR | ZQL             | 59   | 1000 | 336.6       | 336.6      | 31.8        |

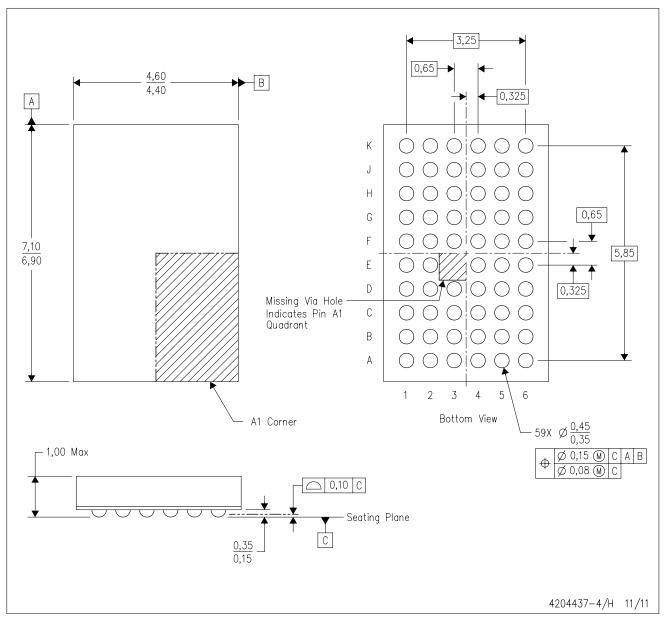

# ZQL (R-PBGA-N59)

## PLASTIC BALL GRID ARRAY

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-285 variation BA-2.

- D. This package is Pb-free.

MicroStar Junior is a trademark of Texas Instruments

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>